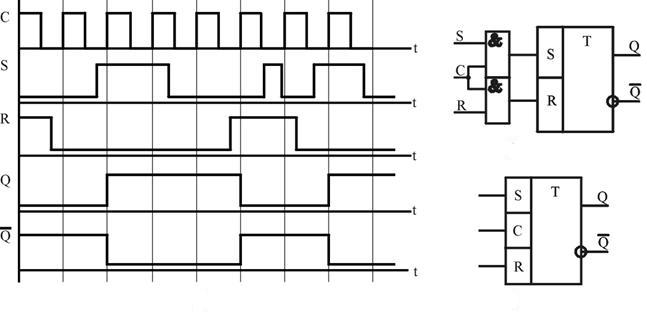

2. Синхронний RS-тригер на основі логічних елементів

АБО-НІ

Рис. 12. Схема

синхронного тригера RS, побудованого на

логічних елементах

АБО-НІ.

|

C |

R |

S |

Q |

|

Пояснення |

|

1 |

x |

x |

Q(t-1) |

|

Режим зберігання інформації |

|

0 |

1 |

1 |

Q(t-1) |

|

Режим зберігання інформації |

|

0 |

1 |

0 |

1 |

0 |

Режим запису одиниці |

|

0 |

0 |

1 |

0 |

1 |

Режим запису нуля |

|

0 |

0 |

0 |

- |

- |

Заборонена комбінація |

Рис. 13. Таблиця

істинності синхронного RS-тригера (4 АБО-НІ).

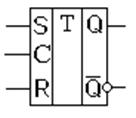

Синхронні RS-тригери можуть бути реалізовані на різних логічних елементах. При цьому логіка роботи синхронних RS-тригерів не змінюється. В той же самий час тригери часто випускаються у вигляді готових мікросхем (або реалізуються всередині ВІС у вигляді готових модулів), тому на принципових схемах синхронні тригери зазвичай зображуються у вигляді умовно-графічних позначень. Умовно-графічне позначення синхронного RS-тригера приведене на рисунку.

Рис. 14.

Умовно-графічне позначення синхронного RS-тригера.

Рис. 15. Часова діаграма, що пояснює роботу синхронного RS-тригера, побудованого на логічних елементах І-НІ.