Тема 4. Синхронний JК-тригер

План

1.

Призначення та будова синхронного JК-тригера.

2. Лічильний

режим JК-тригера.

1. Призначення та будова синхронного JК-тригера

Перш ніж

почати вивчення JК-тригера, пригадаємо принципи

роботи RS-тригера. В цьому тригері є заборонені комбінації вхідних сигналів.

Одночасна подача одиничних сигналів на входи R і S заборонені.

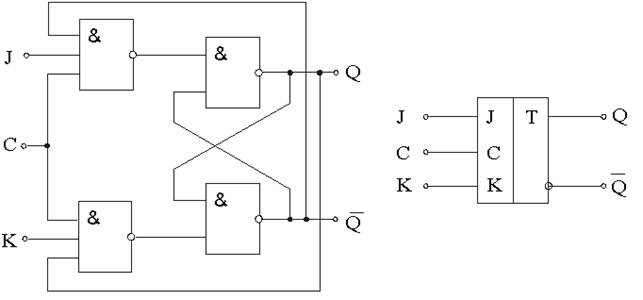

Простий JК-тригер можна отримати з синхронного RS-тригера, якщо

ввести додаткові зворотні зв'язки з виходів тригера на входи, які дозволяють

усунути невизначеність в таблиці істинності.

При вхідних

сигналах J=K=0

стан тригера не змінюється, оскільки напруга низького рівня на одному вході

елементу І-НІ відміняє проходження сигналів від інших його входів і утримує

вихідний сигнал на високому рівні. Якщо на входи J і K подати взаємно протилежні рівні, то

при подачі перепаду напруги на вхід С виходи JК-тригера

встановлюються такі ж стани. При подачі на входи J і K одночасно напруги високого рівня

тригер перемикається в стан, протилежний попередньому, якщо на вхід

синхронізації С подати перепад напруги.

Рис. 16. Синхронний JK-тригер.

Таблиця

істинності синхронного JK-тригера

практично збігається з таблицею істинності синхронного RS-тригера. Для того,

щоб виключити заборонений стан, схема тригера змінена таким чином, що при

подачі двох одиниць JK-тригер

перетворюється на лічильний тригер. Це означає, що при подачі на тактовий вхід

C імпульсів JK-тригер

змінює свій стан на протилежний.

|

C |

K |

J |

Q(t) |

Q(t+1) |

Пояснення |

|

0 |

x |

x |

0 |

0 |

Режим

зберігання інформації |

|

0 |

x |

x |

1 |

1 |

|

|

1 |

0 |

0 |

0 |

0 |

Режим

зберігання інформації |

|

1 |

0 |

0 |

1 |

1 |

|

|

1 |

0 |

1 |

0 |

1 |

Режим

установки одиниці J=1 |

|

1 |

0 |

1 |

1 |

1 |

|

|

1 |

1 |

0 |

0 |

0 |

Режим

запису нуля K=1 |

|

1 |

1 |

0 |

1 |

0 |

|

|

1 |

1 |

1 |

0 |

1 |

K=J=1

рахунковий режим тригера |

|

1 |

1 |

1 |

1 |

0 |

Рис. 17. Таблиця істинності

синхронного JK-тригера.