Тема 3. Синхронний RS-тригер

План

1. Синхронний RS-тригер (4 І-НІ).

2. Синхронний RS-тригер (4 АБО-НІ).

1.

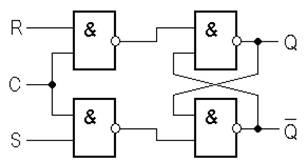

Синхронний RS-тригер на основі логічних елементів І-НІ

Схема

RS-тригера дозволяє запам'ятовувати стан логічної схеми, але оскільки в

початковий момент часу може виникати перехідний процес, то запам'ятовувати

стани логічної схеми потрібно лише в певні моменти часу, коли всі перехідні

процеси закінчені.

Це означає,

що більшість цифрових схем вимагають сигналу синхронізації (тактового сигналу).

Всі перехідні процеси в комбінаційній логічній схемі повинні закінчитися за час

періоду синхросигналу, що подається на входи

тригерів. Тригери, що запам'ятовують вхідні сигнали лише у момент часу,

визначений сигналом синхронізації, називаються синхронними.

Синхронні

тригери забезпечуються додатковим входом, по якому поступає синхронізуючий

сигнал. При цьому зміна стану тригера відбувається лише в ті моменти часу, коли

на спеціальний синхронізуючий вхід тригера поступає синхроімпульс.

Синхронізуючий вхід позначається буквою С.

Рис. 10. Схема синхронного RS-тригера,

побудованого на логічних елементах І-НІ.

Принцип

роботи RS-тригера не змінився, додалася додаткова умова: синхронізація моменту

спрацьовування схеми. В таблиці істинності символ x означає, що значення логічних

рівнів на даному вході не важливі. Вони не впливають на роботу тригера.

|

C |

R |

S |

Q |

|

Пояснення |

|

0 |

x |

x |

Q(t-1) |

|

Режим

зберігання інформації |

|

1 |

0 |

0 |

Q(t-1) |

|

Режим

зберігання інформації |

|

1 |

0 |

1 |

1 |

0 |

Режим

запису одиниці |

|

1 |

1 |

0 |

0 |

1 |

Режим

запису нуля |

|

1 |

1 |

1 |

- |

- |

Заборонена

комбінація |

Рис. 11. Таблиця істинності

синхронного RS-тригера (4 І-НІ).