Для апаратної реалізації булевих виразів використовується деякий набір

логічних елементів [5], які випускаються у вигляді інтегральних мікросхем

(ІМС). Існують спеціалізовані ІМС, які розроблені методами інтегральної

технології спеціально для отримання необхідної логічної залежності. Спеціалізовані

ІМС не потребують ніяких паяних з’єднань і мають високу надійність. Однак

розробка схожих мікросхем економічно виправдана лише при великому об’ємі

випуску. Прикладом може слугувати масовий випуск спеціалізованих ВІС для

електронних годинників, мікрокалькуляторів тощо.

Крім спеціалізованих ІМС, існує універсальний набір логічних елементів у

вигляді ІМС, які забезпечують реалізацію будь-яких логічних функцій. До цього

набору можна віднести: інвертор; кон’юнктор; диз’юнктор; повторювач; І-НІ;

АБО-НІ; виключаючи АБО; сумування за модулем два (непарність); сумування за

модулем два з відмовою (парність); еквівалентність; нееквівалентність;

І-АБО-НІ; заборона та ін.

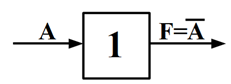

4.1 Інвертор (логічний

елемент «НІ»)

Інвертор

реалізує логічну функцію:

![]() . (4.1)

. (4.1)

Нижче показані його позначення на електричних схемах (рисунок. 4.1, а) і

принципова схема (рисунок 4.1,б).

а)

б)

Рисунок 4.1 – Схема логічного елемента «НІ» на транзисторній базі:

а) – функціональна; б) – принципова

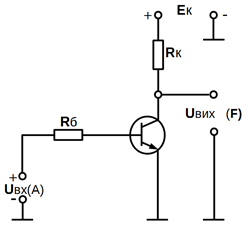

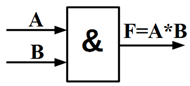

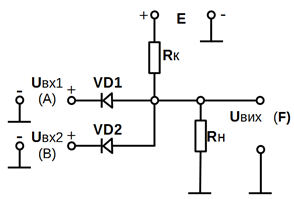

4.2 Кон’юнктор

(логічний елемент «І»)

Кон’юнктор

реалізує логічну функцію:

![]() .

(4.2)

.

(4.2)

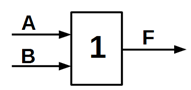

Нижче показані (наведені) його позначення на електричних схемах

(рисунок 4.2, а), принципова схема (рисунок 4.2, б) і таблиця істинності

(таблиця 4.1).

а б

Рисунок 4.2 – Схема логічного елемента «І» на діодній елементній базі:

а) функціональна схема; б) принципова схема

Таблиця 4.1.

Таблиця істинності

|

№ набору |

B |

A |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

|

2 |

1 |

0 |

0 |

|

3 |

1 |

1 |

1 |

Термін «логічний», зазвичай, використовують по відношенню до процедури

прийняття рішення. В такому випадку, можна сказати, що логічний елемент – це

така схема, яка базується на вхідних сигналах, «може вирішувати», що їй

відповісти на виході – «так» або «ні». Схема кон’юнктора на рисунку 4.2, б

відповідає «так» (на виході з’являється високий рівень напруги) тільки в такому

випадку, коли на обидва її входи подані сигнали «так» (обидві вхідні напруги

мають високий рівень).

На рисунку 4.3 показана схема дослідження логічного елемента «І» в

лабораторних умовах.

Входи логічного елемента підключені до ключів SA1 і SA2.

Індикатором виходу служить світлодіод. Якщо на входах А і В виникають сигнали

низького логічного рівня (земля), то світлодіод не випромінює. Цю ситуацію

відображає перший рядок таблиці 4.2.

Рисунок 4.3 – Функціональна схема двовхідного логічного елемента «І» з

індикацією вихідного сигналу

Таблиця 4.2 – Таблиця істинності

|

№ рядка |

Вхід |

Вихід |

||||

|

B |

A |

F |

||||

|

Рівень напруги |

Двоякий сигнал |

Рівень напруги |

Двоякий сигнал |

Випромі-нювання |

Двоякий сигнал |

|

|

1 |

Низький |

0 |

Низький |

0 |

Ні |

0 |

|

2 |

Низький |

0 |

Високий |

1 |

Ні |

0 |

|

3 |

Низький |

1 |

Низький |

0 |

Ні |

0 |

|

4 |

Високий |

1 |

Високий |

1 |

Є |

1 |

Крім значень рівнів напруги і відмітки наявності випромінювання, вхідні і

вихідні сигнали в таблиці 4.2 позначені двоякими (двійковими) числами: 0 і 1.

Згідно з рядком 1, якщо на обидва входи подані двоякі нулі, то на виході

логічного елемента також виникає двоякий нуль. Двояка одиниця на виході

елемента І з’являється тільки в тому випадку, коли на обидва входи А і В подані

двоякі одиниці.

Двоякій одиниці, або напрузі високого рівня, в точках А, В або F відповідає

потенціал +5В віносно землі. Двоякий нуль, або напруга низького рівня, в точках

А, В або F відповідають потенціалу землі (точніше, близько до потенціалу землі,

тобто до нуля). Ми використовуємо тут так звану «позитивну логіку», оскільки

для отримання двоякої одиниці використовується позитивна напруга +5В. При

роботі з цифровими електронними пристроями ми частіше за все будемо мати справу

з «позитивною логікою».

4.3 Диз’юнктор

(логічний елемент «АБО»)

Диз’юнктор

реалізує логічну функцію

![]() .

(4.3)

.

(4.3)

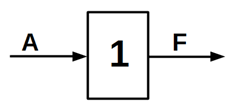

Нижче показані його позначення на електричних схемах (рисунок. 4.4,а),

принципіальна схема (рисунок. 4.4,б) і таблиця істинності (таблиця 4.3).

Таблиця 4.3

Таблиця істинності

|

№ набору |

B |

A |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

2 |

1 |

0 |

1 |

|

3 |

1 |

1 |

1 |

Відмінність логічного елемента «АБО» полягає в тому, що на його виході

з’являється сигнал низького рівня тільки тоді, коли на всі його входи подаються

також сигнали низького логічного рівня.

а) б)

Рисунок 4.4 – Схема логічного елемента «АБО» на діодній елементній базі:

а) функціональна схема; б) принципова схема

![]() (4.4)

(4.4)

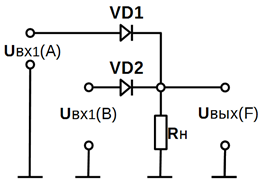

Його позначення на електричних схемах показано на рисунку 4.5.

Рисунок. 4.5 – Функціональна схема повторювача

Повторювач не виконує ніяких логічних перетворень і використовується для

підвищення завантажувальної здатності окремих виходів ІМС або виконує функцію

елемента затримки, яка рівна часу поширення сигналу через нього.

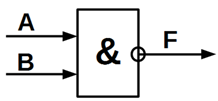

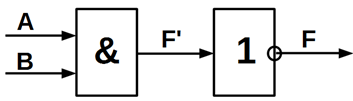

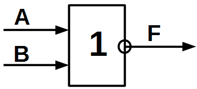

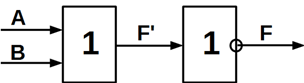

Елемент І-НІ

реалізує логічну функцію:

![]() . (4.5)

. (4.5)

Нижче наведені його позначення на електричних схемах [3] (рисунок 4.6, а),

принципіальна схема (рисунок 4.6, б) і таблиця істинності (таблиця 4.4).

Таблиця 4.4 –

Таблиця істинності

|

№ набору |

B |

A |

F |

|

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

|

2 |

1 |

0 |

1 |

|

3 |

1 |

1 |

0 |

а б

Рисунок 4.6 – Функціональні схеми

логічного елемента «І-НІ», які виконані в різних формах

Елемент АБО-НІ

реалізує логічну функцію:

![]() (4.6)

(4.6)

Нижче показані його позначення на електричних схемах

(рисунок. 4.7,а), принципова схема (рисунок. 4.7,б) і таблиця істинності

(таблиця 4.5).

Таблиця 4.5 – Таблиця істинності

|

№ набору |

B |

A |

F |

|

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

0 |

|

2 |

1 |

0 |

0 |

|

3 |

1 |

1 |

0 |

Рисунок 4.7 – Функціональна схема логічного елемента «АБО-НІ», виконаного в

різних формах

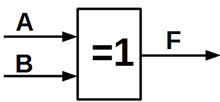

4.7 Логічний елемент

«Виключаючи АБО»

![]() (4.7)

(4.7)

Нижче наведені

його позначення на електричних схемах (рисунок 4.8), і таблиця істинності

(таблиця 4.6).

Таблиця 4.6 – Таблиця істинності

|

№ набору |

B |

A |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

2 |

1 |

0 |

1 |

|

3 |

1 |

1 |

0 |

Елемент називається «виключаючи АБО», його таблиця істинності співпадає з

таблицею істинності елемента АБО першими трьома рядками. В четвертому рядку

елемента АБО F=1, а елемента «виключаюче

АБО» – нуль.

Нижче наведена таблиця істинності перемикаючої функції «виключаючи АБО» для

3-х-вхідних логічних змінних (таблиця 4.7).

Рисунок

4.8 – Функціональна схема логічного

елемента «Виключаючи АБО»

Таблиця 4.7 –

Таблиця істинності 4.7

|

№ набору |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

|

4 |

1 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

1 |

|

7 |

1 |

1 |

1 |

0 |

4.8 Логічна функція

«сумування за модулем два» (непарність)

Елемент

реалізує логічну функцію:

![]() . (4.8)

. (4.8)

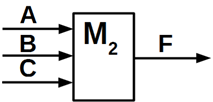

Нижче показані його позначення на електричних схемах (рисунок 4.9) і

таблиця істинності (таблиця 4.8).

Таблиця 4.8 – Таблиця істинності трьох змінних

|

№ набору |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

1 |

|

3 |

0 |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

0 |

|

6 |

1 |

1 |

0 |

0 |

|

7 |

1 |

1 |

1 |

1 |

Елемент сумує значення змінних за модулем два (символ Å (псевдоплюс) означає Smod2: 0 + 0 = 0; 1 + 1 = 0; 1 + 0 = 1; 0 + 1 = 1).

Якщо при сумуванні число одиниць непарне, то функція рівна 1, в

протилежному випадку – F=0.

Рисунок 4.9 – Функціональна схема

логічного елемента, який реалізує функцію «сумування

за модулем 2»

4.9 Логічна функція

«сумування по модулю два» з відмовою (парність)

Елемент

реалізує логічну функцію:

![]() (4.9)

(4.9)

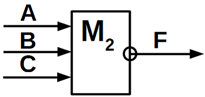

Нижче наведені його позначення на електричних схемах (рисунок 4.10) і

таблиця істинності (таблиця 4.9).

Рисунок 4.10 – Функціональна схема

логічного елемента, який реалізує функцію «сумування

за модулем 2» з відмовою

Елемент формує суму за модулем два, яка потім інвертується на виході. Якщо

при сумуванні число одиниць парне, то функція рівна 1, у протилежному випадку –

F=0.

Таблиця 4.9 – Таблиця істинності трьох змінних

|

№ набору |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

2 |

0 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

1 |

|

4 |

1 |

0 |

0 |

0 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

1 |

|

7 |

1 |

1 |

1 |

0 |

4.10 Логічна функція «Еквівалентність»

Елемент

реалізує логічну функцію

![]() (4.10)

(4.10)

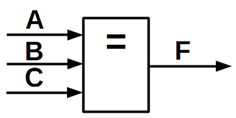

Нижче наведені його позначення на електричних схемах (рисунок 4.11) і

таблиця істинності (таблиця 4.10).

Функція рівна одиниці, коли всі змінні одинакові (рівні одиниці або нулю).

В протилежному випадку – F = 0.

Рисунок 4.11 – Функціональна схема

логічного елемента, який реалізує функцію «еквівалентність»

Таблиця 4.10 – Таблиця істинності трьох змінних

|

№ набору |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

2 |

0 |

1 |

0 |

0 |

|

3 |

0 |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

0 |

|

5 |

1 |

0 |

1 |

0 |

|

6 |

1 |

1 |

0 |

0 |

|

7 |

1 |

1 |

1 |

1 |

4.11

Логічна функція «Нееквівалентність»

Елемент

реалізує логічну функцію:

![]() . (4.11)

. (4.11)

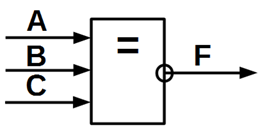

Нижче наведені його позначення на електричних схемах (рисунок 4.12) і

таблиця істинності (таблиця 4.11).

Таблиця. 4.11 – Таблиця істинності

|

№ набору |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

1 |

|

2 |

0 |

1 |

0 |

1 |

|

3 |

0 |

1 |

1 |

1 |

|

4 |

1 |

0 |

0 |

1 |

|

5 |

1 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

1 |

|

7 |

1 |

1 |

1 |

0 |

Функція рівна одиниці, за якої всі змінні неоднакові. У протилежному

випадку – F= 0.

Якщо число логічних змінних рівне двом, то логічна функція і елемент

«нееквівалентність» співпадає з елементами «сума по модулю два» [3] і

«виключаючи АБО» (таблиці 4.6 та 4.7). Тобто, якщо Nпер=2, то:

![]() .

.

Рисунок 4.12 – Функціональна схема

логічного елемента, який реалізує функцію «нееквівалентність»

4.12

Логічна функція «І-АБО-НІ»

Елемент

реалізує більш складну логічну функцію, булевий вираз якої має вигляд:

![]() . (4.12)

. (4.12)

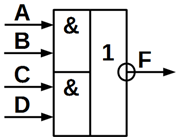

Нижче наведено його позначення на електричних схемах

(рисунок 4.13) і таблиця істинності (таблиця 4.12).

Рисунок 4.13 – Функціональна схема

логічного елемента, який реалізує функцію «І-АБО-НІ»

Таблиця 4.12 – Таблиця істинності

|

№ набору |

D |

С |

В |

А |

F |

|

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

|

2 |

0 |

0 |

1 |

0 |

1 |

|

3 |

0 |

0 |

1 |

1 |

0 |

|

4 |

0 |

1 |

0 |

0 |

1 |

|

5 |

0 |

1 |

0 |

1 |

1 |

|

6 |

0 |

1 |

1 |

0 |

1 |

|

7 |

0 |

1 |

1 |

1 |

0 |

|

8 |

1 |

0 |

0 |

0 |

1 |

|

9 |

1 |

0 |

0 |

1 |

1 |

|

10 |

1 |

0 |

1 |

0 |

1 |

|

11 |

1 |

0 |

1 |

1 |

0 |

|

12 |

1 |

1 |

0 |

0 |

0 |

|

13 |

1 |

1 |

0 |

1 |

0 |

|

14 |

1 |

1 |

1 |

0 |

0 |

|

15 |

1 |

1 |

1 |

1 |

0 |

4.13

Логічна функція «Заборона»

Елемент реалізує

логічну функцію:

![]() . (4.13)

. (4.13)

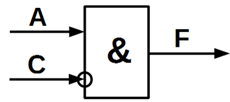

Нижче зазначено його позначення на електричних схемах (рисунок. 4.14) і

таблиця істинності (таблиця 4.13).

Таблиця 4.13 –

Таблиця істинності

|

№ набору |

B |

A |

F |

|

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

2 |

1 |

0 |

0 |

|

3 |

1 |

1 |

0 |

На виході такого елемента логічною одиниця буде лише в тому випадку, якщо

на основному вході присутня логічна одиниця (А=1), а на забороненому вході – нуль (В=0).

У позначенні елемента на електричних схемах заборонений вхід помічений як

інверсний – кружечком. Забороненим сигналом на цьому вході буде логічна

одиниця.

Рисунок 4.14 – Функціональна схема

логічного елемента, який реалізує функцію «ЗАБОРОНА»

4.14 Логічні елементи з

відкритим колектором

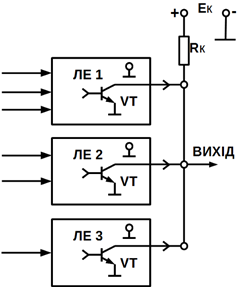

Під час побудови цифрових пристроїв часто виникає необхідність об’єднання

виходів деяких логічних елементів з метою переходу на загальну вихідну пряму.

Цю задачу можна вирішити за допомогою елемента «АБО» (рисунок 4.15).

Рисунок 4.15 – Функціональна схема

логічного елемента, який реалізує функцію «Об’єднуюча

виходи»

При цьому слід наголосити на додаткових схемах затратах і збільшенні

сумарної затримки проходження цифрових сигналів через пристрій [4].

Другий спосіб ґрунтується на використанні логічних елементів із відкритим

колектором, у полі функціонального позначення яких є спеціальний символ ![]() , який вказує, що колектор вихідного

транзистора відкритий (обірваний, «вісить у повітрі»).

, який вказує, що колектор вихідного

транзистора відкритий (обірваний, «вісить у повітрі»).

На рисунку 4.16 показано об’єднання деяких логічних елементів із відкритим

колектором на загальний вихід.

Рисунок 4.16 – Функціональна схема

логічного елемента, який реалізує функцію «Об’єднуюча

виходи» з відкритим колектором

Для нульових сигналів на виходах логічних елементів ЛЕ1…ЛЕ3 (відповідний

вихідний транзистор відкритий) дана схема виконує функцію «монтажне АБО» у разі

появи логічного нуля, за умовами якщо хоча б на одному з виходів логічних

елементів вихідний сигнал також буде рівний нулю.

Для одиничних сигналів на виходах логічних елементів ЛЕ1…ЛЕ3 (відповідний

вихідний транзистор закритий) схема виконує функцію «монтажне І»: вихідний

сигнал рівний одиниці лише за одночасної появи логічних одиниць на виходах всіх

логічних елементів.

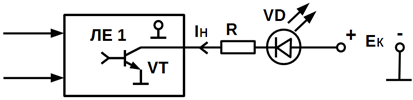

За рахунок технології виготовлення вихідного транзистора і отримання від

нього заданих характеристик, елементи з відкритим колектором мають більш високу

навантажувальну здатність, ніж звичайні ЛЕ, тому можуть використовуватись для

підключення навантажень типу тиристорів, реле, індикаторів (світлодіодів) та

ін. (рисунок 4.17).

Рисунок 4.17 – Функціональна схема

логічного елемента, який реалізує функцію «Об’єднуюча

виходи» з відкритим колектором

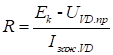

При цьому необхідно забезпечити виконання вимоги:

![]() , (4.14)

, (4.14)

де Iн – струм

навантаження; ![]() – значення допустимого

струму, який може протікати через відкритий вихідний транзистор логічного

елемента (рисунок 4.17).

– значення допустимого

струму, який може протікати через відкритий вихідний транзистор логічного

елемента (рисунок 4.17).

На рисунку 4.18 зображений приклад підключення на вихід ЛЕ з відкритим

колектором світлодіода VD.

Рисунок 4.18 – Функціональна схема

логічного елемента, який реалізує функцію «Об’єднуюча

виходи» з відкритим колектором і світлодіодом

Коли з виходу ЛЕ знімається логічний 0, вихідний транзистор VT відкритий, і

світлодіод VD виявляється ввімкнутим у прямому напрямку. Під час протікання через

VD прямого струму останній запалюється. Струм Iн дорівнює струму запалювання світлодіода Iзаж.VD, який складає £20 mA. Падіння напруги на відкритому діоді UVD.пр складає

(1,7…2) В. Резистор R обмежує величину прямого струму і розраховується за

формулою:

.

(4.15)

.

(4.15)

Наприклад, якщо Ek=5

B; UVD.пр=2 В; Iзаж.VD=20

mA, то R=(5-2)/(20*10-3)=150 Ом.

4.15 Логічні елементи з

третім станом

Один із способів підключення логічних елементів на загальний вихід, який

найбільш широко використовується, заснований на використанні в їх вихідних

ланцюгах електронних буферних схем, здатних під дією керуючих сигналів або

підключати до навантаження вихідний логічний сигнал, який набуває значення

(стану) 0 чи 1, або відключати вихід від навантаження (переводити його в так

званий 3-ій ( Z-стан).

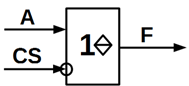

Нижчепоказані: позначення логічного елемента [2, 11] (повторювача) з трьома

станами на електричних схемах (рисунок 4.19, а) і принципова схема його

вихідного каскаду, який забезпечує 3 стани вихідного сигналу: логічний 0;

логічну 1-цю і 3-ій (Z) стан (рисунок 4.19, б).

У полі функціонального значення логічних елементів із трьома станами є

спеціальний символ ![]() .

.

Крім основних входів, на які подаються вхідні логічні змінні, схожі

елементи містять управляючий вхід «Вибір кристала» – CS, активним сигналом на

якому, як правило, є логічний 0 (рисунок 4.19, а).

Три стани вихідних сигналів забезпечуються керуючими сигналами на базах

транзисторів VT1 і VT2 (рисунок 4.19, б):

а) б)

Рисунок 4.19 – Схема повторювача: а) функціональна схема; б) принципова

схема

Одиничний стан – на базі VT1 – одиниця (транзистор – відкритий);

на базі VT2 – нуль (транзистор – закритий) і з виходу знімається логічна 1-ця;

Нульовий стан – на базі VT1 – нуль (транзистор – закритий); на

базі VT2 – одиниця (транзистор – відкритий) і з виходу знімається

логічний 0; Z – стан – на базах VT1 і VT2 – логічні нулі

(обидва транзистора закриті) і вихід зірваний від загальної шини (знаходиться у

Z-стані).

Елементи з трьома станами широко використовуються в мікропроцесорній

техніці для підключення виходів різних приладів мікропроцесорної системи в

загальній шині.

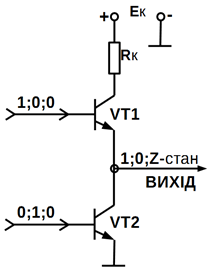

На

рисунку 4.20 показано один із способів узгодження рівнів сигналів, що надходять

від виходу ТТЛ-елемента на вхід КМОН-структури.

У

базовому колі такої транзисторної схеми встановлено 2 резистори, які створюють

вхідний «поріг», що приблизно рівний падінню напруги на 2-х діодах,

забезпечуючи надійну перешкодостійкість. «Пришвидшуючий» конденсатор збільшує

швидкість перемикання. Іноді резистор R2

відсутній і тоді транзистор відкривається при вхідній напрузі, що приблизно

рівна 0,7 В. У даному випадку не забезпечуватиметься достатня

перешкодостійкість.

Рисунок

4.20 – Схема узгодження рівнів сигналів, що надходять

від виходу ТТЛ-елемента

на вхід КМОН-структури

Величина

навантажувального резистора може бути більшою за

меншої

важливості перешкодостійкості. Інакше номінал має вибиратись меншим.

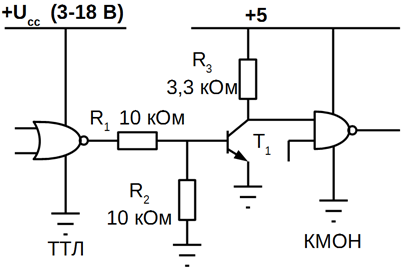

На

рисунку 4.21 бачимо аналогічну ситуацію,

лише проходить зворотнє узгодження від КМОН до ТТЛ.

У

даному випадку ситуація майже аналогічна до першого випадку і навіть каскад є

також інвертуючим.

Мікросхеми серій К176, К561, Кр1561

випускаються в пластмасових корпусах із

дворядним розташуванням 14, 16 або 24 штирьових виводів, а мікросхеми серії 564

–

у

корпусах з тією ж кількістю виходів,

розташованих у

одній плоскості, в так званих планарних

корпусах. Номінальна напруга живлення мікросхем серії К176 – 9 В ±5%, проте вони,

як правило, зберігають працездатність у

діапазоні живлячої напруги від 5 до 12 В. Для мікросхем серій К561 і 564 гарантується

працездатність при напрузі живлення від 3 до 15 В, для Кр1561 – від 3 до 18 В. Діапазон робочих температур мікросхем серії К176 від – 10° до +70 °С , серій

К561 і Кр1561 – від -45° до

+85°С, серії 564 – від -60° до +125°С.

Рисунок

4.21 – Схема узгодження рівнів сигналів, що надходять

від виходу КМОН-структури на вхід ТТЛ-елемента

Вихідні рівні мікросхем, під час роботи на

однотипних мікросхемах практично не відрізняються від

напруги живлення і потенціалу спільного дроту. Максимальний вихідний струм

більшості мікросхем серій К176, К561 і 564 не стандартизований і не перевищує

одиниць міліампер, що дещо

уповільнює безпосереднє узгодження

мікросхем цих серій із якими-небудь індикаторами і мікросхемами ТТЛ-серій.

Характерною особливістю мікросхем серії Кр1561 є наявність буферних елементів

не лише на виходах складних елементів, як у мікросхемах серій К176, К561 і

564, але і на входах, і виходах всіх мікросхем, незалежно від їх складності. Крім того,

в мікросхемах серії Кр1561 покращено захист від перевантажень як на вході, так і на виході, у вихідні

ланцюги додано невеликі струмообмежувальні резистори.

Стандартні статичні характеристики

навантажень мікросхем серії Кр1561 наступні. При логічному 0 на виході і вихідній

напрузі 0,4; 0,5; 1,5 В вихідний впадаючий струм не менше 0,44; 1,1; 3 мА; при

напрузі живлення 5, 10, 15 В

відповідно. Ті ж норми існують і для витікаючих струмів логічної 1 при вихідній напрузі 4,6; 9,5; 13,5 В

відповідно. Крім того, гарантується, що при напрузі живлення 5 В, вихідній

напрузі 2,5 В вихідний витікаючий струм при логічній 1 складе не менше 1,36 мА.

Реально вихідні струми мікросхем

серії Кр1561 значно більше. При логіному 0 на виході і вихідній

напрузі 0,5 В вихідний струм складає приблизно 3...5, 5...10, 6...15 мА при напрузі

живлення 5, 10, 15 В відповідно. Аналогічно витікаючий струм при логічній 1, вихідна напруга на 0,5 В менша, ніж напруга живлення, яка складає

при тій же напрузі живлення приблизно 1,2... 1,5; 2...3;

3...4 мА.

При напрузі на виході 1 В, коли логічний 0, вихідний впадаючий струм складає 6...10,10...20,12...25 мА, коли вказана вище напруга живлення,

на 1 В менша напруга живлення, а при логічній 1 витікаючий струм 2...3,

4...5, 5...7 мА відповідно.

Струм короткого замикання при напрузі 5 В

складає близько 10 мА а при логічному 0 і близько 6 мА – логічній 1, що

дозволяє підключати практично будь-які світлодіоди до виходів мікросхем цієї

серії без обмежувальних резисторів. При напрузі

живлення 10 або 15 В струм короткого замикання може досягати

20...60 мА, тому включення

обмежувальних резисторів необхідне.

Вихідний струм 0,44 мА, коли логічний 0 при напрузі на виході 0,5 В і напрузі живлення 5 В гарантує

нормальну роботу мікросхем серії Кр1561 на один вхід мікросхем серії К555.

Оскільки, як указувалося вище, реальний вихідний струм у цих умовах

більший, мікросхеми серії Кр1561 можна навантажувати на декілька входів

мікросхем серії К555 або на один вхід мікросхеми серії Кр 155.

Напруга живлення на мікросхеми

даних серій подається на вивід із найбільшим номером, спільний дріт

підключається до виводу з удвічі меншим номером. Виняток становлять мікросхеми

К561ПУ4 і Кр1561ПУ4, а також мікросхеми, що вимагають для своєї роботи два джерела

живлення. Всі виключення відмічено далі під час опису конкретних

мікросхем.

Під час

використання мікросхем слід пам'ятати, що захист входів мікросхем діодами від

статичної електрики не є повним. Тому під час монтажу пристроїв із

мікросхемами КМОН необхідно дотримуватися наступних правил.

Для виключення випадкового пробою

за рахунок статичної електрики потенціали вмонтовуваної плати, паяльника і тіла

монтажника мають бути зрівняні. Для цього на ручку паяльника можна намотати

декілька витків неізольованого дроту або укріпити металеву пластинку і з'єднати

через резистор 100...200 кОм з металевими частками паяльника. Звичайно, обмотка

паяльника не повинна мати контакту з його жалом. При монтажі вільною рукою слід

торкатися шин живлення вмонтовуваної плати. Якщо мікросхема знаходиться в

металевій коробці або її виводи упаковані у фольгу, перш ніж узяти мікросхему,

слід доторкнутися до коробки або фольги. При передачі мікросхеми з рук в руки

слід зрівняти потенціали тих, що беруть участь у цьому, доторкнувшись один до

одного до моменту передачі.

Вживання мікросхем КМОН-серій має

свої особливості. Жоден із входів мікросхем не може бути

залишений непідключеним, навіть якщо логічний елемент у мікросхемі

не використаний. Вільні входи елементів повинні бути або сполучені з використовуваними

входами того ж елемента або підключені до шини живлення або до спільного дроту відповідно

до логіки роботи мікросхеми. Напруга джерела живлення повинна подаватися раніше

або одночасно з подачею вхідних сигналів.

У будь-якому пристрої, зібраному на

мікросхемах структури КМОН, рекомендується перед першим включенням перевірити

продзвоном подачу напруги живлення на всі виводи живлення і ті виводи

мікросхем, на які напруга живлення подається відповідно до принципової схеми.

Річ у тому, що мікросхема КМОН через наявність вхідних

захисних діодів може працювати без подачі напруги на виведення живлення, якщо

хоч би на один із входів мікросхеми подано напругу живлення

або логічна 1. Аналогічно слід перевірити ланцюг спільного дроту з тієї ж

причини.

Логіка роботи

мікросхем з однаковим буквенно-цифровим позначенням біля серій К176, К561,

Кр1561 і 564 повністю збігається, як і реальні електричні параметри біля

мікросхем серій К561 і 564, хоча паспортні норми у них різні. Тому тут

розглядуються лише ті мікросхеми серії 564, які або відсутні в інших серіях,

або мають інші буквено-цифрові позначення.

Найбільш швидкодіючими логічними ІМС у даний час є елементи емітерно-зв’язаної

логіки (ЕЗЛ) і особливо елементи

емітерно-зв’язаної логіки з

емітерними повторювачами на вході (ЕЕЗЛ). Ці елементи працюють у режимі переключення струму, і в них

висока швидкодія забезпечується,

насамперед, за рахунок запобігання

насичення транзисторів шляхом введення глибокого

зворотного зв’язку по струму за допомогою резистора в колі емітера.

Цей зворотний зв’язок одночасно сприяє скороченню тривалості перехідних процесів у базі транзисторів. Важливу роль грають обмеження меж зміни перепадів напруги і використання емітерних

повторювачів для введення і знімання інформації.

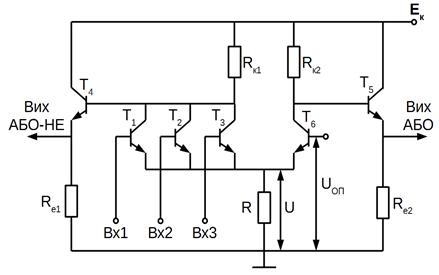

Найбільш

простим елементом на перемикачах струму є елемент ЕЗЛ, схема якого показана на

рисуноку 4.22. Особливості елементів з об’єднаними емітерами зручно пояснити на

прикладі цього елемента.

Рисунок 4.22 – Мікросхема ЕЗЛ

Основу

розглянутої групи ІМС складає перемикач струму, що являє собою ключовий елемент

на транзисторах з об’єднаними емітерами (рисунок 4.22 транзистори T1 —

Тз і Т). У емітерне коло транзисторів задається струм I0 постійного значення. Сталість струму I0 підтримується або шляхом включення в коло емітерів

порівняно високоомічного резистора R або шляхом використання транзисторного

джерела струму. Значення струму I0 вибирають

так, щоб у нормальному режимі роботи елемента вимикається насичення

транзисторів, що утворюють перемикач струму.

Керування перемикачем струму здійснюється шляхом подачі сигналів на бази транзисторів T1 —

Т3. На базу транзистора T подається фіксований опорний потенціал Uоп, значення якого вибирають так, щоб транзистор Т був здатний

пропускати повністю струм I0 у разі встановлення

на базах вхідних транзисторів низького потенціалу, який відповідає логічному 0.

При подачі високого потенціалу, що відповідає логічній 1-ці, на базу хоча б одного

з вхідних транзисторів струм I0 перемикається в емітерне коло відповідного вхідного

транзистора. При цьому транзистор Т з фіксованим зсувом замикається. При

перемиканні елемента відбувається зміна

вихідних потенціалів: потенціал колекторів вхідних транзисторів

знижується, а потенціал колектора транзистора Т, підвищуючи, досягає рівня напруги джерела живлення Ек.

У колі

послідовно включених перемикачів струму колекторні потенціали не можна

безпосередньо використовувати як вхідні

напруги для керування наступними ІМС, тому що вони перевищують рівні

відповідних потенціалів на входах. Для нормальної роботи ІМС необхідно зробити

зрушення рівня колекторних потенціалів. Для цієї мети найбільше часто

використовують емітерні повторювачі, що підключаються до колекторів вхідних

транзисторів і транзистора з фіксованим

зсувом (рисунок 4.22), повторювачі на транзисторах Т4 і Т5. При цьому зрушення рівня дорівнює

перепаду напруги між базою і емітером Uбэ.сд

транзистора. Цим перепадом напруги лімітується розмах логічного сигналу ![]() .

.

Дійсно, на базу вхідного транзистора в провідному стані подається вхідна напруга: ![]() , яка відповідає логічній 1-ці, що призводить до відмикання цього транзистора і

зниження потенціалу колекторів вхідних

транзисторів. При цьому, щоб відкритий транзистор не

насичувався, необхідно забезпечити виконання умови

, яка відповідає логічній 1-ці, що призводить до відмикання цього транзистора і

зниження потенціалу колекторів вхідних

транзисторів. При цьому, щоб відкритий транзистор не

насичувався, необхідно забезпечити виконання умови![]() , що є можливою лише в

тому випадку, якщо перепад напруги на колекторі не перевищує напруги зрушення,

створена повторювачем, тобто, у разі:

, що є можливою лише в

тому випадку, якщо перепад напруги на колекторі не перевищує напруги зрушення,

створена повторювачем, тобто, у разі:

![]()

![]() .

(4.16)

.

(4.16)

Порушення цієї умови призводить до

насичення транзистора,

тому що потенціал його колектора виявляється нижче потенціалу бази. Отже, збільшення розмаху

логічного сигналу, який визначається перепадом напруги в колекторному

колі вхідних транзисторів, припустимо

тільки за відповідного

збільшення зсуву рівня Uбэ.сд.

Цього можна досягти, наприклад,

шляхом вмикання додаткового діода, що зміщає, у емітерні кола транзисторів Т4 і Т5 . Емітерні повторювачі (без зсувних діодів)

забезпечують зсув рівня, що складає 0,8–0,9 В. Розмах логічного сигналу, дорівнює цьому значенню,

виявляється достатнім для більшості цифрових автоматів, побудованих на елементах ЕЗЛ. При цьому, для того, щоб одержати однаковий розмах

логічного сигналу на інвертуючому і

неінвертуючому виходах елемента

значення опорів резисторів RKl

=RK2 вибираються рівними один одному: RKl =RK2 = RK.

Включення повторювачів призводить також до зменшення вихідного

опору елемента, що сприяє підвищенню його навантажувальної здатності і

швидкодії. Таким чином,

перемикач струму, доповнений емітерними повторювачами, стає логічним елементом,

що реалізує операції АБО-НІ і АБО. Сигнал, що відповідає операції АБО-НІ, знімається з

виходу повторювача, підключеного до інвертуючої половини елемента (тобто, до

колекторів вхідних транзисторів), а сигнал, що відповідає операції АБО, — з

виходу повторювача, зв’язаного з транзистором Т .

Елементи на перемикачах струму

виготовляються у вигляді напівпровідникових

чи сполучених ІМС. Так як в цих ІМС

транзистори працюють без насичення, то шляхом підключення підкладки та ізолюючих шарів до точок відповідно

з найменшим і найбільшим потенціалами можна замкнути паразитні транзистори,

вимкнувши тим самим їх активну дію. Тому в ІМС на перемикачах струму

виявляється тільки ємнісний вплив підкладки.

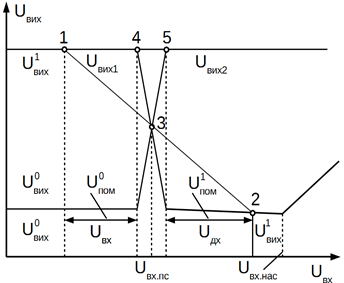

На рисунку 4.23 показано перемикальну характеристику

мікросхеми ЕЗЛ для двох її виходів:

інвертуючого (Uвых1) та неінвертуючого (Uвых2).

Рисунок 4.23 – Перемикальні

характеристики мікросхеми ЕЗЛ

При вхідних напругах, менших за потенціал відмикання, вхідні

транзистори залишаються замкненими і на інвертуючому встановлюється високий потенціал:

![]() . (4.17)

. (4.17)

Відповідний логічна 1 (lес.– число

вхідних транзисторів). При цьому струм I0

цілком відбирається транзистором Т із

фіксованим зсувом і на неінвертуючому виході установлюється низький потенціал:

![]() , (4.18)

, (4.18)

відповідний логічний 0. Розмах логічного сигналу:

![]() (4.19)

(4.19)

Коли

напруга UВХ досягає потенціалу відмикання, вхідні транзистори

починають проводити, і струм I0 частково

відгалужується в емітери провідних транзисторів. Якщо одночасно проводять lпр вхідних транзисторів

(із загального числа lэс), то потенціал

колектора цих транзисторів зменшується і

відповідно знижується напруга на інвертуючому виході до рівня:

![]() (4.20)

(4.20)

Через

перерозподіл струму I0

змінюється і напруга на

неінвертуючому виході:

![]() (4.21)

(4.21)

Струми

емітерів Іэ1 і Іэ

відповідно для вхідних транзисторів і

транзистора Т визначаються

співвідношеннями:

![]() (4.22)

(4.22)

![]() (4.23)

(4.23)

де U0 = IoR – потенціал об’єднаних емітерів

відносно

загальної шини живлення.

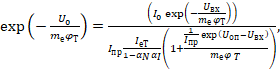

У разі

відмикання вхідних транзисторів несуттєво

змінюється струм I0 і відповідно потенціал

об’єднаних емітерів U0. Зміна струму I0 настільки незначна,

що ними можна знехтувати. Не так істотно змінюється і потенціал U0 (у порівнянні зі своїм середнім

значенням). Однак, ця незначна зміна U0 порівнюється з напругою на емітерних переходах транзисторів. Саме вона призводить

до зміни струму емітера Іе

транзистора з фіксованим зсувом, тому для

правильного розрахунку перемикальної

характеристики ![]() необхідно враховувати зміну U0 зі зміною вхідної напруги Uвх. Залежність U0 про від Uвх можна визначити із рівняння:

необхідно враховувати зміну U0 зі зміною вхідної напруги Uвх. Залежність U0 про від Uвх можна визначити із рівняння:

І0 = ІпрІе1+

Іе, представивши його в наступному вигляді:

![]() . (4.24)

. (4.24)

Визначивши із цього рівняння:

(4.25)

(4.25)

можна виразити залежність вихідних напруг від вхідної напруги наступними співвідношеннями:

![]() , (4.26)

, (4.26)

![]() . (4.27)

. (4.27)

У разі зміни вхідної напруги іншого вигляду набуває і різниця потенціалів Uбе.сд на емітерному переході

транзисторів у схемах повторювачів. Тому що в робочому діапазоні відхилення Uбе.сд від

свого середнього значення незначні, то при практичних розрахунках ними можна зневажати,

прийнявши:

![]() . (4.28)

. (4.28)

Це значення Uбэ.сд

відповідає середньому значенню струму емітера транзистора в схемі повторювача, який визначається зі співвідношення:

![]() , (4.29)

, (4.29)

де ![]() .

.

Тому що ![]() та

та ![]() визначаються через

визначаються через ![]() , то при первісних розрахунках зручно замість формули

(4.24) скористатися

співвідношенням:

, то при первісних розрахунках зручно замість формули

(4.24) скористатися

співвідношенням:

![]() , (4.30)

, (4.30)

заснованим на рівності Uоп =0,5(![]() +

+ ![]() ),

до виконання якого звичайно

прагнуть, щоб забезпечити симетрію елемента по граничних напругах.

),

до виконання якого звичайно

прагнуть, щоб забезпечити симетрію елемента по граничних напругах.

Коли транзистор Т перестає проводити, струм І0 цілком відбирається провідними вхідними

транзисторами. Після цього зі збільшенням вхідної напруги спостерігається

зменшення напруги на

інвертуючому виході Uвих.1. Тому що після повного

переключення струму І0

провідні вхідні транзистори працюють із глибоким негативним зворотним зв'язком по струму, що протікає через

резистор R, то зменшення Uвих.1 незначне. При напрузі Uвх.нас. транзистори насичуються, їхній базовий струм

відгалужується в колекторний ланцюг, зменшуючи перепад напруги на RK1, тому Uвих1 зростає (рисунок 4.23). Насичення вхідних транзисторів порушує нормальний режим роботи ІМС, тому шляхом відповідного підбору параметрів схеми і напруг джерел живлення такий режим роботи вимикається.

Як видно з графіків (рисунок 4.23), перемикальні

характеристики Uвих.1 і Uвих.2 перетинаються в точці 3, координати якої можна визначити з рівняння Uвих.1= Uвих.2. На

підставі цього рівняння можна показати, що перемикальні характеристики перетинаються при

вхідній напрузі:

![]() . (4.31)

. (4.31)

При

цьому:

![]() , (4.32)

, (4.32)

тобто, в

точці перетину:

![]() . (4.33)

. (4.33)

Якщо

опорна напруга обрана рівною середньому значенню ![]() та

та ![]() , тобто:

, тобто:

![]() , (4.34)

, (4.34)

де робочі

точки 1 і 2 розташовуються симетрично щодо середньої точки 3 для lпр = 1.

Тому що в

мікросхемі ЕЗЛ транзистори працюють у активній області у всьому робочому

діапазоні зміни вхідної напруги, де перешкодостійкість обмежується напругою, за

якої коефіцієнт підсилення логічного елемента відповідними виходами зростає до

1-ці. На підставі (4.23) можна показати, що коефіцієнт підсилення по

інвертуючому виходу стає рівним мінус одиниці ![]() при вхідній

напрузі:

при вхідній

напрузі:

![]() (4.35)

(4.35)

а по неінвертуючому виходу – одиниці ![]() , коли вхідна напруга досягає:

, коли вхідна напруга досягає:

![]() . (4.36)

. (4.36)

Коефіцієнт

К визначається виразом:

![]() . (4.37)

. (4.37)

Перешкодостійкість ІМС, яка визначається як різниця

вхідних напруг у робочих струмах і при одиничному коефіцієнті підсилення, розраховується за

формулами:

![]() , (4.38)

, (4.38)

![]() , (4.39)

, (4.39)

які виходять на

підставі формул, виведених вище. Зазначено, що при lпр=1 перешкодостійкість для логічної 1 і логічного 0 по входу

виявляється однаковою. Зі збільшенням числа провідних транзисторів lпр симетрія ІМС по перешкодостійкості порушується; перешкодостійкість для

логічної 1-ці стає більше

перешкодостійкою для логічного 0.

Під час визначення навантажувальної здатності і

коефіцієнта об'єднання по входу в ІМС на перемикачах струму припустимі значення

перешкодостійкості не є визначальними, як це має місце для інших типів логічних

елементів. Для розглянутої

групи ІМС зазначені параметри визначаються припустимим збільшенням тривалості

перехідних процесів, тому що ІМС на перемикачах струму є швидкодіючими і саме

цей параметр для них є визначальним.

Підвищення швидкодії елемента ЕЗЛ досягається шляхом помітного збільшення споживаної

потужності. Середнє значення цієї потужності можна розрахувати за формулою:

![]() (4.40)

(4.40)

у який перший

доданок ![]() – це потужність, споживана перемикачем струму, а

другий доданок

– це потужність, споживана перемикачем струму, а

другий доданок ![]() – середня потужність, споживана емітерними повторювачами. Виразивши на підставі (4.28) напругу Ек через Uоп,

– середня потужність, споживана емітерними повторювачами. Виразивши на підставі (4.28) напругу Ек через Uоп, ![]() Uлог та Uбе.сд , одержимо:

Uлог та Uбе.сд , одержимо:

![]() . (4.41)

. (4.41)

Подальше удосконалення

логічних елементів на перемикачах струму призвело до розробки ІМС емітерно-зв’язаної логіки з емітерними повторювачами на вході (скорочено ЕЕЗЛ-елементи).

У мікросхемі елемента ЕЗЛ (рисунок. 4.22)

емітерні повторювачі вмикаються до виходів елемента для знімання інформації.

При цьому перемикач струму

складається з вхідних транзисторів, що використовуються для введення інформації і транзистора з опорною напругою.

До виходу кожного повторювача підключають

транзистори, кожний з яких є вхідним елементом наступних перемикачів струму.