ЛАБОРАТОРНА РОБОТА № 2

Тема: Основи

булевої алгебри та двійкові логічні елементи .

Мета роботи: вивчити закони булевої алгебри

та принципи роботи основних мікро-електронних логічних елементів.

1. Теоретичні відомості

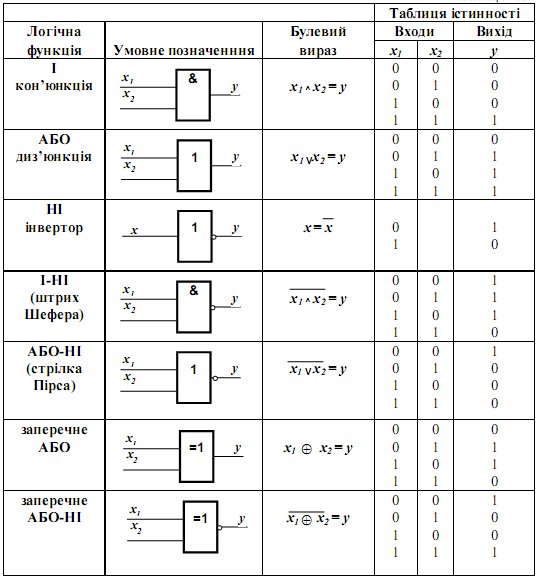

Основні логічні

функції, умовні позначення та таблиці істинності зображені на таблиці 2.1, що

також містять і відповідний булевий вираз.

Таблиця

2.1

У мікросхемах

побудованих на основі логічних елементів часто бувають входи, що не

використовуються.

Тому на практиці із

входами, що не використовуються чинять так :

- об’єднують із

входами, які використовуються із урахуванням функцій, що виконують-ся даним

входом;

- у тих випадках, коли

на вході, що не використовується повинен бути логічний «0», вказаний вхід

просто з’єднують із загальною шиною живлення;

- для створення рівня

логічної «1» напруга на вході повинна бути в межах 2.4-3.6 В. Безпосередньо

підключати виходи ТТЛ-мікросхем до напруги живлення неможна, внаслідок великого

вхідного струму І1вх.

Логічну «1» на входах

ТТЛ-мікросхем забезпечують одним із таких способів :

- підключають до виходу

вільного елемента (найчастіше до І-НЕ, входи якого з’єднані із загальною шиною)

максимальну кількість входів, які необхідно підключити до елемента. Ця

кількість обмежується його навантажувальною здатністю;

- входи, що не

використовуються, приєднуються до свого джерела живлення через обмежувальні

резистори 1-2кОм. До цього резистора можна під’єднувати до 20 входів ТТЛ серії

К155;

- входи ТТЛ мікросхем,

що не використовуються повинні містити логічну «1». В край-ньому разі їх можна

залишати вільними. Тоді завдяки струмам витоку на них встановлюється потрібна

напруга. Проте такий спосіб веде до зменшення швидкодії та завадостійкості.

2. Практична частина

Під’єднання виводів

потрібно здійснювати ретельно, без розривів. Адже тоді можлива неправильна

робота схеми. Для зручності під’єднань можна застосовувати «крапку». Її

вста-новлення на схемі у потрібних місцях дає можливість краще проектувати

складні вузли.

2.1.

Програма роботи та завдання.

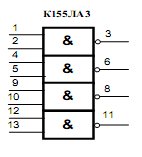

2.1.1. Скласти схему мал. 2.1

за допомогою програми EWB

5 на компонентах І-НЕ.

2.1.2. Дослідити правильність

роботи спроектованої схеми.

2.1.3. Визначити можливі

вихідні комбінації, заповнивши таблицю 2.2.

2.1.4. Зробити висновки на

основі таблиці.

2.1.5. Відповісти письмово на

контрольне питання.

Мал.2.1

Таблиця

2.2

|

Вихідна комбінація |

0 0 0 0 |

0 0 0 1 |

0 0 1 0 |

0 0 1 1 |

0 1 0 0 |

0 1 0 1 |

0 1 1 0 |

0 1 1 1 |

1 0 0 0 |

1 0 0 1 |

1 0 1 0 |

1 0 1 1 |

1 1 0 0 |

1 1 0 1 |

1 1 1 0 |

1 1 1 1 |

|

Одна з відповідних вхідних комбінацій |

1 1 1 1 1 1 1 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 0 0 0 0 0 0 0 |

Контрольні питання:

1)

Що чинять на практиці із входами логічних

елементів, які не використовуються?