Тема 10. Елементна база з реалізації

базових логічних елементів

Для

побудови цифрових пристроїв найбільш широке застосування знаходять інтегральні

логічні елементи на базі ТТЛ -, ТТЛШ -, ЕСЛ - і КМОН-технологій. Будь-яка

мікросхема, що реалізує складну функцію, за суттю являє сукупність елементів І–НЕ або АБО–НЕ.

7.1 Базовий ТТЛ (ТТЛШ)-елемент І–НЕ

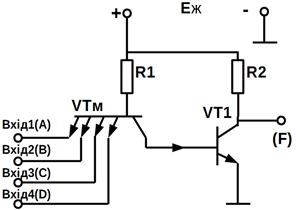

Найпростіший

ТТЛ-елемент [2], назва якого розшифровується як транзисторно-транзисторна

логіка, складається з кон'юнкторного, виконаного на багато-емітерному транзисторі

VТМ і транзисторного інвертора VT1

(рисунок 7.1).

Рисунок

7.1 – Схема найпростішого ТТЛ-елемента

При

високих рівнях напруги на всіх виходах схеми (логічна 1) всі переходи емітер –

база багатоемітерного транзистора VTМ зміщуються у зворотному напрямку

(замкнені), а перехід база – колектор за рахунок напруги + Ежив – у

прямому (інверсне включення транзистора). Струм колекторного переходу

транзистора VТМ, що протікає через перехід емітер – база транзистора VТ1,

вводить останній у режим насичення. При цьому з виходу знімається низький

рівень напруги (логічний нуль). Якщо хоча б на один вхід схеми надійде сигнал

логічного 0 (низький рівень напруги), VТМ відкривається і на базу VТ1 подається

низький рівень напруги. Останній закривається і з виходу знімається високий

рівень сигналу (логічна одиниця). Таким чином, елемент реалізує логічну функцію

І – НЕ (![]() ).

).

Вихідний

опір розглянутого елемента залежить від стану транзистора VТ1. Коли він

відкритий, воно близько до нуля, а коли замкнений – ![]() .

.

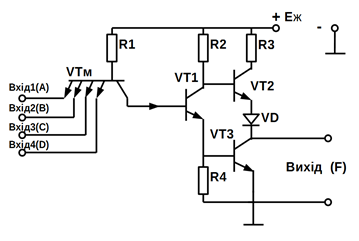

Для

підвищення завадостійкості та збільшення навантажувальної здатності

ТТЛ-елементи містять додаткові транзистори (рисунок 7.2).

Рисунок

7.2 – Принципова схема для підвищення завадостійкості на базі ТТЛ

Подібна

схема називається ТТЛ-елементом зі складним інвертором, виконаним на трьох

транзисторах VT1, VT2 і VT3. Якщо на всіх входах елемента присутня логічна

1-ця, то емітерний перехід VТМ замкнений, а колекторний – відкритий. Струм бази

VТМ через перехід “база – колектор” VTМ надходить до бази VT1. У результаті VT1

входить у режим насичення. Позитивним потенціалом, що знімається з резистора R4,

транзистор VT3 відкривається і з виходу схеми знімається логічний 0. Завдяки

наявності діода VD транзистор VT2 при цьому надійно закритий.

Діод

забезпечує додатковий позитивний приріст напруги на емітер VT2 і зміщується.

Використання таких діодів – один з типових прийомів інтегральної технології, що

дозволяє забезпечити надійне замикання вимкнених транзисторів. Наявність

замкненого VT2 у колекторного ланцюга відкритого VT3 практично виключає

споживання струму вихідним ланцюгом складного інвертора в стані спокою (без

навантаження). Навантаження, включене між + Ежив і колектором VT3 може викликати чималий струм (![]() ).

).

Якщо хоча

б на один вхід схеми (рисунок 7.2) надійде логічний 0, то транзистор VТМ

насичується, на його колекторі (базі VT1) з'являється низький рівень напруги і

транзистор VT1 замикається. Потенціал його емітера прагне до нуля, а потенціал

колектора – до напруги + Ежив. Транзистор VT3 закривається, VT2 –

відкривається. З виходу знімаємо високий рівень напруги (логічна 1-ця). Каскад

на транзисторі VT2 працює в активному режимі як емітерний повторювач (значення

резистора R3 мало (десятки Ом) і може не враховуватися). Вихідний опір

емітерного повторювача дуже малий, тому навантажувальна здатність другої схеми

(рисунок. 7.2) в порівнянні з першою (рисунок. 7.1) значно збільшується.

Споживання

струму в вихідному ланцюзі ненавантаженого складного інвертора в цьому стані

також мало, так як VT3 закритий. Якщо між виходом (колектором VT3) і корпусом

включити опір навантаження, то споживаний схемою струм збільшується (![]() ).

).

Відсутність

власного споживання струму вихідним ланцюгом складного інвертора робить

розглянутий елемент досить економічним.

Разом з

тим, ця схема має істотний недолік. Під час формування логічної одиниці на

виході струм закритого транзистора VT3 Iкоз протікає через резистор

R4 (рисунок 7.2), створюючи на ньому падіння напруги, спрямоване на відмикання

транзистора. Щоб знизити цю напругу значення резистора R4 береться не дуже

великим (сотні Ом).

Мале

значення R4 шунтує перехід база – емітер VT3 під час його відмикання.

Наприклад, під час напруги ![]() В через

резистор R4 = 1 кОм протікає струм

0,6 мА. Отже, VT3 відкривається тільки після того, як струм через резистор R4

зростає до 0,6 мА. Це призводить до розтягування в часі перехідної області

передавальної характеристики елемента, що розглядається.

В через

резистор R4 = 1 кОм протікає струм

0,6 мА. Отже, VT3 відкривається тільки після того, як струм через резистор R4

зростає до 0,6 мА. Це призводить до розтягування в часі перехідної області

передавальної характеристики елемента, що розглядається.

Крім

того, наявність R4 впливає на стабільність параметрів ТТЛ-елемента в робочому

діапазоні температур. Цей резистор має позитивний температурний коефіцієнт

опору (ТКС). За зростання температури значення R4 збільшується, його шунтуюча

дія зменшується, струм бази VT3 збільшується, транзистор VT3 насичується

сильніше, що може збільшити час його виключення, тобто, погіршує швидкодію. За

зниження температури значення R4 падає, його шунтуюча дія зростає, що

призводить до збільшення часу включення.

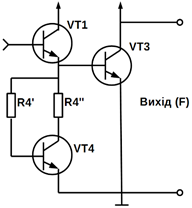

Для

усунення зазначених недоліків замість резистора R4 в схему

ТТЛ-елемента увімкнений нелінійний чотириполюсний (рисунок 7.3), виконаний на

транзисторі VT4.

Це

дозволяє зменшити тривалість перехідної області передавальної характеристики

ТТЛ-елемента і підвищити стабільність його параметрів.

Розглянута

схема зі складним інвертором також реалізує функцію І – НІ.

Рисунок

7.3 – Принципова схема нелінійного чотириполюсника дозволяє підвищити

стабільність базової схеми ТТЛ

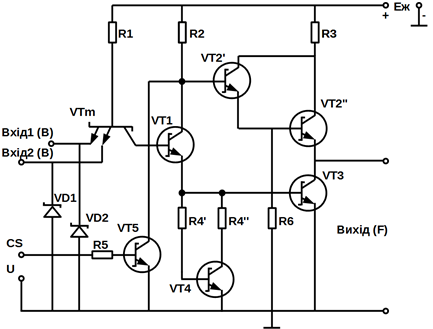

ТТЛ-схеми

в даний час досить широко застосовуються в модифікованому ТТЛШ-виконанні і

містять транзистори і діоди Шотткі (рисунок 7.4).

Нижче

показаний приклад двовхідного логічного ТТЛШ-елемента І – НЕ (рисунок 7.4), що

має ряд додаткових елементів, відсутніх у розглянутій вище ТТЛ-схемі (рисунок 7.2).

По-перше,

для підвищення навантажувальної здатності замість транзистора VТ 2 (рисунок

7.2) у схему введений складовий транзистор (VТ2 ', VТ2 ").

По-друге, для захисту елемента від випадково поданих негативних вхідних

сигналів у нього включені діоди VD1, VD2. По-третє, схема містить транзистор

VТ5, за допомогою якого здійснюється переказ виходу схеми в третьому, (Z) –

стан (див. 4.15). Позитивний потенціал (лог. 1-ця) на базі транзистора VТ5

відкриває його, замикаючи тим самим колектор транзистора VТ1 на землю.

Рисунок

7.4 – Принципова схема двовхідного логічного елемента «І – НЕ», який виконаний

на елементній базі ТТЛШ

Це

призводить до того, що транзистори VТ2 ', VТ2 " і VТ3 залишаються

замкнені, незалежно від стану вхідних керуючих сигналів. При цьому вихід F

відключається як від шини живлення, так і від землі, тобто, ніби зависає в

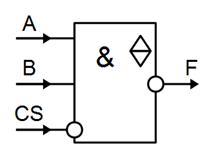

повітрі. Функціональне позначення такого логічного елемента показано на рисунку

7.5.

Рисунок 7.5 – Функціональне

позначення логічного елемента

Можливість переведення ТТЛ (ТТЛ)-схем у третьому стані дозволяє

використовувати їх під час роботи на одну системну шину, наприклад, у

мікропроцесорних пристроях. При цьому до загальної шини підключений цілий ряд

різних пристроїв, які мають вихідні кола з трьома станами, причому в кожен

момент часу із загальною шиною з'єднаний тільки один пристрій, а виходи інших

знаходяться в 3-му (Z)-стані, тобто, відключені від шини.

7.2 Базовий ЕЗЛ-елемент АБО / АБО – НІ

У цьому елементі [3, 11] логічні операції виконуються емітерно-пов'язаними

транзисторами, чим і обумовлена назва типу логіки. Елемент має два виходи, на

одному з яких фіксується результат операції АБО над вхідними цифровими

сигналами, а на іншому – операції АБО – НЕ.

У цій схемі до "землі" приєднана плюсова шина джерела живлення,

тому вихідні сигнали мають негативну полярність.

Розроблені на основі схем ЕЗЛ ІМС характеризуються високою швидкодією,

великою навантажувальною здатністю, низькою завадостійкістю і досить значною

споживаною потужністю.

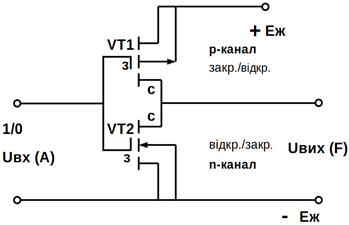

7.3 Базовий КМОН-елемент АБО–НІ

Логічні схеми, виконані на базі комплементарного метал-оксидного

напівпровідника (доповнюють один одного) МОН (МДП)-транзисторах, містять

послідовно включені і керовані одним сигналом МОН-транзистори з каналами різних

типів провідності (n- і p-типу) (рисунок 7.6).

Коли один з послідовно включених транзисторів відкривається, інший – закривається. Тому такий

каскад практично не споживає потужності в статичному режимі.

КМОН-елемент (рисунок 7.6) являє собою дільник напруги + Ежив.

Нижнє плече дільника становить транзистор VT2, який називається комутуючим або

керуючим. Верхнє плече утворює транзистор VT1, який називається

навантажувальним. Якщо на вхід подається високий рівень напруги (лог. 1-ці), то

відкривається транзистор VT2 і закривається VT1. Велика частина напруги

живлення виділяється на навантажувальному транзисторі VT1, а з виходу

знімається низький рівень напруги (логічний 0).

Рисунок 7.6 – Принципова схема логічного елемента, який виконаний на

елементній базі КМОН

Якщо на вхід надходить низький рівень сигналу (логічний 0), то

відкривається VT1 і закривається VT2. З виходу знімається високий рівень

напруги, а відкритий транзистор VT1 виконує функцію стокового резистора Rс.

Розглянута схема виконує функцію інвертора.

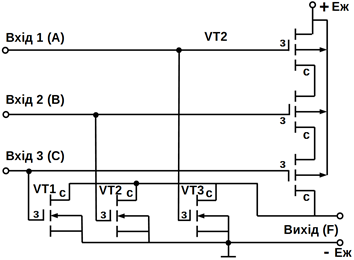

Нижче показана схема логічного елемента з трьома входами АБО – НЕ на КМОН-транзисторах

(рисунок. 7.7).

Рисунок 7.7 – Принципова схема двовхідного логічного елемента «АБО – НІ»

Якщо на будь-який із входів, наприклад, С, подається високий рівень

(логічна 1-ця), то відкривається транзистор VT1 і шунтує паралельно включені з

ним транзистори VT2 і VT3. Опір нижнього плеча дільника, що складається з трьох

паралельно включених керуючих транзисторів VT1, VT2 і VT3, зменшується.

Одночасно замикається транзистор VT6 і опір верхнього плеча дільника, що

складається з трьох послідовно включених навантажувальних транзисторів VT4, VT5

і VT6 стає досить значним. Велика частина напруги живлення + Ежив виділяється на навантажувальних транзисторах, а з

виходу знімається низький рівень сигналу (логічний 0).

Тільки коли на всіх входах А, В і

С присутній низький рівень сигналу

(логічний 0), керуючі транзистори закриті, а навантажувальні – відкриті. Падіння

на навантажувальних транзисторах мале і вони виконують функцію стокового

(навантажувального) резистора Rс для паралельно включених закритих

транзисторів VT1 ... VT3. З виходу знімається високий рівень напруги

(логічна 1-ця).

Таким чином, розглянутий елемент (рисунок. 7.7) виконує логічну функцію АБО

– НІ:

![]() . (7.1)

. (7.1)

Логічні КМОН-елементи мають ряд істотних переваг. По-перше, в статичному

стані в ланцюзі джерела Ежив

знаходиться замкнений транзистор, так що споживана елементом потужність дуже

мала. Споживання потужності відбувається тільки у разі перемикання елемента.

По-друге, вхідний опір польового транзистора дуже великий, тому кожен наступний

елемент практично не навантажує попередній. По-третє, під час виконання за

інтегральною технологією польовий транзистор займає на підкладці (підставі

мікросхеми) меншу площу, ніж біполярний. Недоліком елемента є менша швидкодія,

ніж у ТТЛШ – та ЕЗЛ-елементів.

Під час перевезення й монтажу у КМОН-схемах потрібно дотримуватися певних

запобіжних заходів. Зокрема, монтажник і всі монтажні інструменти повинні бути

заземлені, щоб виключити можливість пробою ізоляції між затвором і каналом.