Лабораторна робота №

7

Тема: Дослідження роботи електронної схеми

синхронного

D-тригера.

Мета: Експериментально визначити усі можливі

стани електронної

схеми синхронного D-тригера.

Теоретичні відомості.

D-тригер називають інформаційним тригером, також тригером затримки. D-тригер буває тільки синхронним.

Тригер має один інформаційний вхід D, і один синхронізуючий вхід С.

Одна із можливих структурних схем однотактного D-тригера і його умовне позначення наведені на рисунку.

Рис. 27. Схема та

умовне позначення синхронного D-тригера.

Якщо рівень сигналу на вході С=0, стан тригера стійкий і не залежить від рівня сигналу на інформаційному вході. При подачі на вхід синхронізації рівня С=1 інформація на прямому виході буде повторювати інформацію, що подається на вхід D.

В такому тригері відбувається затримка сигналу на виході по відношенню до сигналу, поданого на вхід, під час паузи між синхросигналами. Для стійкої роботи тригера необхідно, щоб протягом синхроімпульса інформація на вході була незмінною.

Потенційне і

динамічне управління D-тригера.

Синхронні D-тригери можуть бути з потенційним і динамічним управлінням. У перших з них інформація записується протягом часу, при якому рівень сигналу С=1. В тригерах з динамічним управлінням інформація записується тільки протягом перепаду напруги на вході синхронізації. Динамічні входи зображають на схемах трикутником. Якщо верхівка трикутника звернута в сторону мікросхеми, то тригер «спрацьовує» по фронту вхідного імпульсу, якщо від неї - по зрізу імпульсу. В такому тригері інформація на виході може бути затримана на один такт по відношенню до вхідної інформації.

В популярній вітчизняній мікросхемі К155ТМ2 міститься два незалежних D-тригери з входами скидання і установки, R і S відповідно.

Рис. 28. Мікросхема

К155ТМ2.

Обладнання.

1. Персональний комп’ютер.

2. Система автоматизованого проектування Electronics Workbench 10.

3. Бібліотека електронних елементів.

Порядок виконання

роботи.

1. Запустити САПР Electronics

Workbench 10, відкрити файл бібліотеки електронних елементів (Рис. 29).

2. Скласти

електронну схему синхронного D-тригера (Рис. 27).

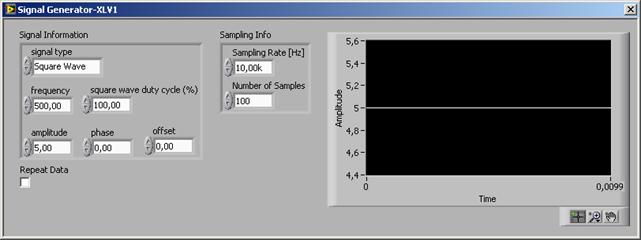

Джерело живлення

схеми – генератор високочастотних коливань (XLV1) (Рис. 30). Джерело

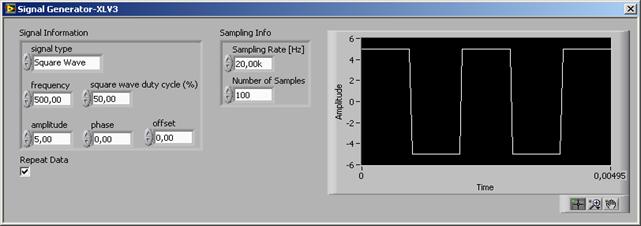

синхроімпульсів – генератор високочастотних коливань (XLV2) (Рис. 31). Від

генераторів через ключі (key) сигнали потрапляють на схему логічних елементів.

Входи електронної схеми з’єднані з світловими індикаторами (LED), які показують

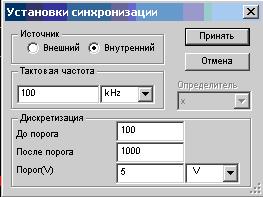

рівень сигналу (0 чи 1), а виходи з’єднані з логічним аналізатором (XLA1) (Рис.

32).

3. Візуально

перевірити правильність складання схеми.

4. Скопіювати

складену електронну схему із САПР Electronics

Workbench 10 у лабораторну роботу, помістивши її перед контрольними

запитаннями.

5. Експериментально

визначити можливі стани електронної схеми за допомогою графіка логічного

аналізатора.

6. Скопіювати

графік логічного аналізатора із САПР Electronics Workbench 10 у лабораторну роботу, помістивши її перед

контрольними запитаннями.

Рис. 29. Бібліотека

електронних елементів САПР Electronics

Workbench 10.

Рис. 30. Налаштування генератора

високочастотних коливань (XLV1).

Рис. 31. Налаштування генератора

високочастотних коливань (XLV2).

Рис. 32. Налаштування логічним аналізатором

(XLA1).