Лабораторна робота №

5

Тема: Дослідження роботи електронної схеми

синхронного JK-тригера.

Мета: Експериментально визначити усі можливі

стани електронної

схеми синхронного JK-тригера.

Теоретичні відомості.

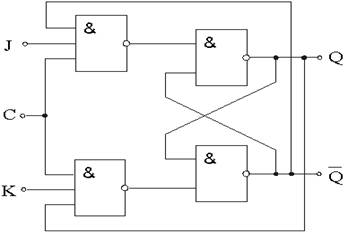

Простий JК-тригер можна отримати з синхронного RS-тригера, якщо ввести додаткові зворотні зв'язки з виходів тригера на входи, що дозволяє усунути невизначеність у таблиці істинності.

При вхідних сигналах J=K=0 стан тригера не змінюється, оскільки напруга низького рівня на одному вході елемента І-НІ відміняє проходження сигналів від інших його входів і утримує вихідний сигнал на високому рівні. Якщо на входи J і K подати взаємно протилежні рівні, то при подачі перепаду напруги на вхід С виходи JК-тригера встановлюються такі ж стани. При подачі на входи J і K одночасно напруги високого рівня тригер перемикається в стан, протилежний попередньому, якщо на вхід синхронізації С подати перепад напруги.

Таблиця істинності JK-тригера практично збігається з таблицею істинності синхронного RS-тригера. Для того, щоб виключити заборонений стан, схема тригера змінена таким чином, що при подачі двох одиниць JK-тригер перетворюється на лічильний тригер. Це означає, що при подачі на тактовий вхід C імпульсів JK-тригер змінює свій стан на протилежний.

Рис. 17. Синхронний JK-тригер.

Обладнання.

1. Персональний комп’ютер.

2. Система автоматизованого проектування Electronics Workbench 10.

3. Бібліотека електронних елементів.

Порядок виконання

роботи.

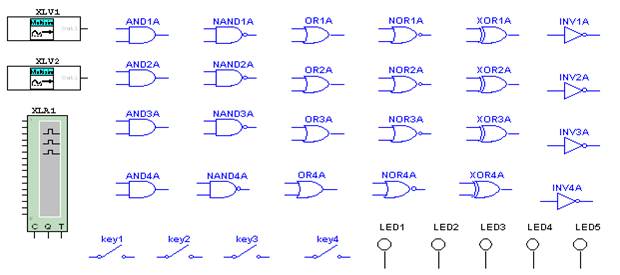

1. Запустити САПР Electronics

Workbench 10, відкрити файл бібліотеки електронних елементів (Рис. 18).

2. Скласти

електронну схему синхронного JK-тригера (4 І-НІ) (Рис. 17).

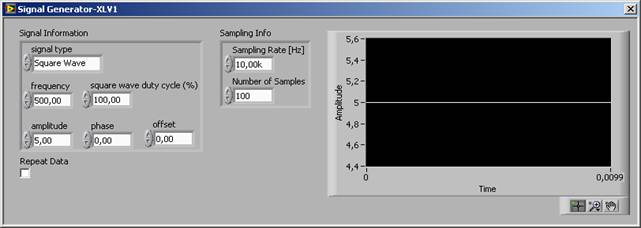

Джерело живлення

схеми – генератор високочастотних коливань (XLV1) (Рис. 19). Джерело

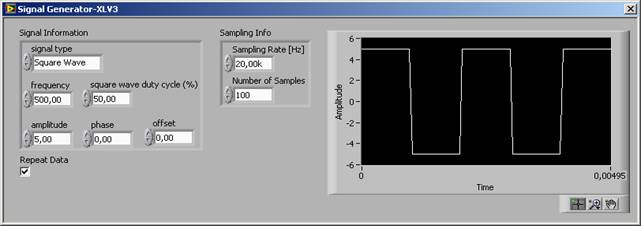

синхроімпульсів – генератор високочастотних коливань (XLV2) (Рис. 20). Від

генераторів через ключі (key) сигнали потрапляють на схему логічних елементів.

Входи електронної схеми з’єднані з світловими індикаторами (LED), які показують

рівень сигналу (0 чи 1), а виходи з’єднані з логічним аналізатором (XLA1) (Рис.

21).

3. Візуально

перевірити правильність складання схеми.

4. Скопіювати

складену електронну схему із САПР Electronics

Workbench 10 у лабораторну роботу, помістивши її перед контрольними

запитаннями.

5. Експериментально

визначити можливі стани електронної схеми за допомогою графіка логічного

аналізатора.

6. Скопіювати

графік логічного аналізатора із САПР Electronics Workbench 10 у лабораторну роботу, помістивши її перед

контрольними запитаннями.

Рис. 18. Бібліотека

електронних елементів САПР Electronics

Workbench 10 для лабораторної роботи № 5.

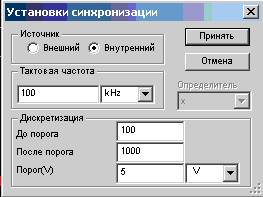

Рис. 19. Налаштування генератора

високочастотних коливань (XLV1).

Рис. 20. Налаштування генератора

високочастотних коливань (XLV2).

Рис. 21. Налаштування логічним аналізатором

(XLA1).

Контрольні запитання.

1. Які особливості в будові синхронного JK-тригера Вам відомі?

2. В чому різниця в принципах функціонування між синхронним RS-тригером

та синхронним JK-тригером?