2. Паралельні

регістри (статичні)

В паралельному регістрі на синхронних D-тригерах (рис. 29) код числа, що запам‘ятовується, подається на інформаційні входи всіх тригерів і записується в регістр з приходом тактового імпульсу. Вихідна інформація змінюється з подачею нового вхідного слова і приходом наступного імпульсу запису. Такі регістри використовують в системах оперативної пам'яті. Число тригерів в них дорівнює максимальній розрядності слів, що зберігаються у ньому.

Рис. 29. Паралельний

регістр на синхронних D-тригерах.

Послідовні регістри

(зсуву)

Схема послідовного регістра і часова діаграма, що ілюструє його роботу, наведені на рис. 30. З приходом тактового імпульсу С перший тригер записує код Х (0 або 1), що знаходиться в цей момент на його вході D, а кожний наступний тригер перемикається в стан, в якому до цього знаходився попередній. Так відбувається тому, що сигнал, який записується, проходить із входу D тригера до виходу Q із затримкою, більшою тривалості зміни тактового імпульсу (протягом якого відбувається запис). Кожний тактовий імпульс послідовно зсуває код числа у регістрі на один розряд. Тому для запису N-розрядного коду необхідно N тактових імпульсів. На діаграмі видно, що чотирирозрядне число 1011 було записане у відповідні розряди регістра (1 - Q4, 0 - Q3, 1 - Q2, 1 - Q1) після приходу четвертого тактового імпульсу. До приходу наступного тактового імпульсу це число зберігається в регістрі у виді паралельного коду на виході Q4-Q1. Якщо необхідно отримати інформацію, що зберігається у послідовному коді, то її знімають із виходу Q4 в моменти приходу наступних чотирьох імпульсів (5-8). Такий режим називається режимом послідовного зчитування.

Рис. 30. Послідовний

регістр.

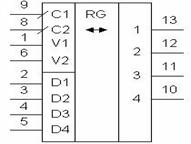

Дуже зручні універсальні регістри, що дозволять здійснювати як послідовний, так і паралельний запис і зчитування. Такі регістри можна використовувати як перетворювачі паралельного коду в послідовний і навпаки. Наприклад, мікросхема К555ИР1 (рис. 31) - чотирирозрядний універсальний зсувний регістр. Регістр працює в режимі зсуву по тактових імпульсах, що надходять на вхід С1, якщо на вході V2 є напруга низького рівня. Вхід V1 служить для введення інформації в перший розряд регістра в цьому режимі. Якщо ж на вході V2 напруга високого рівня, то регістр здійснює паралельний запис інформації із входів D1-D4 по імпульсах синхронізації, що надходять на вхід С2.

Рис. 31.

Чотирирозрядний зсувний регістр (мікросхема К555ИР1).