ЛАБОРАТОРНА РОБОТА № 17-18

Тема: Дослідження демультиплексорів і

дешифраторів.

Мета

роботи. Вивчити принципу роботи та експериментальне дослідження

демульти-плексорів і дешифраторів у інтегральному виконанні; проаналізувати

отримані результати.

1. Теоретичні відомості

Демультиплексори

в функціональному аспекті протилежні мультиплексорам. Тут сиґнали з одного

інформаційного входу розподіляються в потрібній послідовності по декількох

виходах. Вибір потрібної вихідної шини забезпечується задаванням відповідного

коду на адресних входах. Якщо є m адресних входів, демультиплексор,

залежно від конструкції, може мати до 2m виходів. Логічна

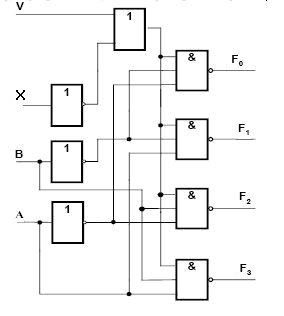

структура простого демультиплексора зображена на мал. 3.1.

Мал.

3.1

Таблиця істинності показана нижче.

Таблиця 3.1

Дешифратором

(декодером) називають пристрій з декількома входами та виходами, у якому певним

комбінаціям вхідних сиґналів відповідає активний стан одного з виходів.

Дешифратор можна розглядати як демультиплексор, у якому адресні входи стали

інформаційними, а колишній інформаційний вхід, на який подається напруга

певного рівня (U0 або U1), підтримує

напругу вихідних виводів в активному стані.

Якщо

в демультиплексора (1:4) на інформаційному вході підтримувати потенціал U0,

або на вході дозволу U1, то пристрій працюватиме як

дешифратор 2:4. Отже, між двома типами цих пристроїв нема принципової

різниці, а відмінність зводиться до виду сиґналів на поодиночному вході: якщо

він змінюється в часі - це демультиплексор, якщо ні - це дешифратор. У

дешифраторів цього входу досить часто нема, а вихідні сиґнали на активному

виході мають одне значення, яке є наперед відоме.

2. Практична частина

Під’єднання виводів потрібно

здійснювати ретельно, без розривів. Адже тоді можлива неправильна робота схеми.

Для зручності під’єднань можна застосовувати «крапку». Її вста-новлення на

схемі у потрібних місцях дає можливість краще проектувати складні вузли.

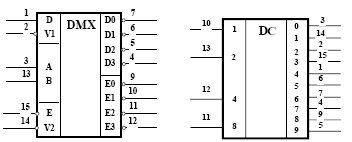

Мал.3.2. Мікросхеми К155ИД4 та

К564ИД1 зліва направо.

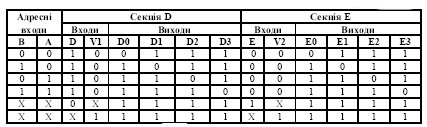

Таблиця 3.2.

Таблиця 3.3.

Мікросхема

К155ИД4 містить в одному корпусі два

демультиплексори-дешифратори. Кожна секція має один інформаційний вхід та один

вхід дозволу. Інформаційний вхід однієї секції (ввід 1) - прямий, а другої -

інверсний (ввід 15). Два адресні входи А

та В - загальні для двох секцій.

Кожна

секція має по чотири виходи D0 - D3 i E0 - E3. Активним рівнем

вихідних сиґналів є U0вих.

Залежно від схеми включення, мікросхема може бути використана в таких режимах:

два демультиплексори «з однієї лінії на

4»; два дешифратори «з двох ліній

на 4»; демультиплексор «з

однієї лінії на 8»; дешифратор «з трьох ліній на 8». Умовне графічне позначення мікросхеми К155ИД4 зображене на мал. 3.2.

Два

дешифратори «з двох ліній на 4»

(2:4) можна одержати, якщо входи А

та В використовувати як

інформаційні, тоді V1 та D (для однієї секції ) і V2 та Е - (для другої секції) будуть

входами дозволу.

Мультиплексори

КМОН-структури, завдяки двонапрямленим ключам, можуть працювати і як

демультиплексори, і як дешифратори. Інформаційні виводи таких мікросхем

позначають як входи/виходи. Керують ними так само, як мультиплексорами.

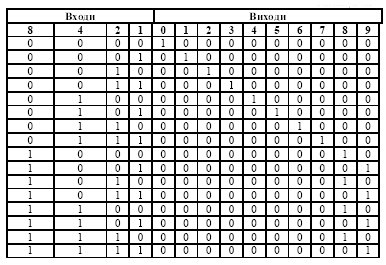

Мікросхема

К564ИД1 використовується для

перетворення двійково-десяткового коду в десятковий, або - двійкового у

вісімковий. Вона має чотири вхідних та десять вихідних виводів (мал. 3.2).

Двійково-десятковий код подається з урахуванням розрядності на входи 1, 2,

4, 8. Кожному наборові відповідає потенціал високого рівня U1вих на одному з десяти

виходів, згідно з таблицею істинності (табл.9.3). З цієї таблиці випливає, що з

появою логічної «1» на вході вищого розряду 8 (вивід 11),

на виходах з номерами від 0 до 7 не виникає рівня логічної «1».

Ця властивість дає змогу використовувати мікросхему як демультиплексор «один до

8» або дешифратор трирозрядного двійкового коду з входом дозволу. У

цьому випадку вхід 8 є інформаційний, а імпульсні сиґнали, які виникають

на цьому вході, повторюються з інверсією на активному виході.

Під

час роботи в режимі трирозрядного дешифратора вхід 8 використовується як

вхід дозволу. Якщо на цей вхід подати низький логічний рівень, то відбувається

декодування сиґналів, які надходять на входи 1, 2, 4. Стан

логічної «1» забороняє вісімкове перетворення і на виходах 0 -

7 з’являється рівень логічний «0».

2.1.

Програма роботи та завдання.

2.1.1. Побудувати схему

мал.3.1 та перевірити її роботу за таблицею істинності. У звіт занести схему

мал.3.1., таблицю 3.1, а також логіку роботи даного демультиплексора.

2.1.2. Вивчити принцип роботи

дешифратора та демультиплексора, побудувати таблицю істинності та схему (на

основі логічних елементів) вигляду «2 в 4» для подвійного

дешифратора-демультиплексора мікросхеми К155ИД4.

2.1.3. Вивчити принцип роботи

та виписати у звіт таблицю істинності дешифратора на основі мікросхеми К564ИД1.

2.1.4. Навести короткий

приклад застосування дешифратора або демультиплексора.

2.1.5. У звіт занести усі схеми,

вихідні дані, вимірювані та розраховані дані. Відповісти письмово на контрольні

питання.